# Superconducting Materials and Devices for Future High-Performance Non-von Neumann Computers

## Harrison A. Walker<sup>1\*</sup> and Michael C. Hamilton<sup>2</sup>

<sup>1</sup>Undergraduate Student, Department of Materials Engineering, Auburn University <sup>2</sup>James B. Davis Professor, Department of Electrical and Computer Engineering, Auburn University

Current computational systems have been primarily based on industry-dominant complementary metaloxide-semiconductor (CMOS) technology for many decades. Most computers are organized according to the von Neumann architecture in which the processor and memory must communicate with one another to process information. This architecture experiences a bottleneck in information flow that restricts the speed of computation. In the age of big data, this presents a limiting factor for the many computational tasks rooted in machine learning. Alternative platforms being investigated must be highly scalable, demonstrate lower power consumption, and perform at higher levels of speed and efficiency than current systems. Neuromorphic hardware takes inspiration from the human brain and is organized with processing and memory distributed throughout the whole system, aiming to reduce the inherent latency in von Neumannlike systems.

A Von Neumann (or Princeton) architecture has been the basis of most computational systems since its conception. [1] This architecture employs a central processing unit (CPU) that works alongside a dedicated memory that stores data and instructions together. The processor and memory must communicate with each other to process information, requiring the movement of data and instructions, leading to an information flow bottleneck that provides one limitation for the speed of computation. Non-von Neumann computing attempts to distribute both processing and memory throughout the whole system with the goal of reducing the inherent latency found in von Neumann-like systems. Neuromorphic computing attempts to mimic the human brain and is organized with both processing and memory distributed among the system. It has been claimed that efficient emulation of scalable biological neural

\*Corresponding author: haw0022@auburn.edu

networks could allow for computation that negates the information bottleneck associated with von Neumannlike architectures and provide a low-power platform more apt for neural networks and parallel processing. [5] Novel neuromorphic circuit elements based on superconducting niobium nitride nanowires have been proposed for use in the implementation of physical neural networks. [3] [2].

In a superconducting 1D nanowire, quantum phase slip (QPS) causes the wire to demonstrate an insulating, zero-current state when an applied voltage is below a critical value and to exhibit resistive behavior when above. [6] Quantum phase slip junctions (QPSJs) are superconductive promising electronic devices for applications high-speed in and low-power neuromorphic computing. Coherent quantum phase slip events can be leveraged by overdamping of QPSJs to create individual quantized current pulses, which are analogous to neuron spiking events in the human brain. Through the implementation of synapse circuitry, nonvolatile memory can be realized through spike-timingdependent plasticity, a biological learning mechanism. [4] Simulation of these circuit elements shows promise, but fabrication challenges have hindered the realization of useful devices. To advance these technologies, this undergraduate research fellowship project explored process development for superconducting NbN nanowire fabrication.

NbN thin films were grown on intrinsic silicon substrates using electron beam evaporation deposition techniques. The photoresist PMMA 950K A2 was then spin-coated onto the wafer. Nanowires were patterned into the resist using an electron beam lithography (EBL) system. Nanowires of lengths ranging from 0.38  $\mu$ m to 1.84  $\mu$ m and widths of 60 nm and 70 nm were patterned to test fabrication capabilities. After EBL, unfocused argon ion milling was used as a physical etching process to remove exposed NbN and leave behind the nanowires. Parameters such as argon flow rate, acceleration voltage, time, and angle of incidence were varied to determine optimal parameters. Etching was characterized by utilizing atomic force microscopy and scanning electron microscopy.

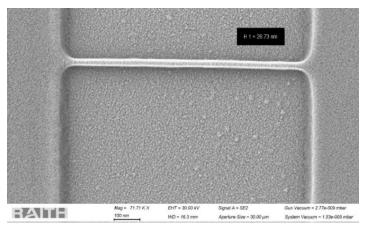

Although difficulties such as disconnections, surface roughness, and polymer crosslinking posed issues during fabrication, the smallest nanowire achieved was 26.73 nm. The nanowire is pictured in figure 1. Electron beam lithography and ion milling as a fabrication process show promise for the manufacturing of ultrathin nanowires for use as quantum phase slip junctions.

#### **Statement of Research Advisor**

The year-long undergraduate research fellowship project that Mr. Walker has described, focusing on a relatively new type of superconductive electronic device, called a quantum phase slip junction (QPSJ), is very exciting and has significant implications for future computing technologies. Superconducting computing has shown promise of exceptionally high-speed and exceedingly low power dissipation compared to conventional computing. Mr. Walker has performed experimental work to help us to better understand the materials and fabrication processes needed to create useful QPSJ devices for future superconductive electronics.

-Michael C. Hamilton, Electrical and Computer Engineering

Fig. 1 Fabricated NbN Nanowire

#### References

[1] Burks, A. W., Goldstine, H. H., and Von Neumann, J. (1982). Preliminary discussion of the logical design of an electronic computing instrument. In *The Origins of Digital Computers* (Springer). 399–413

[2] Cheng, Ran, Uday S. Goteti, and Michael C. Hamilton. "High-speed and low-power superconducting neuromorphic circuits based on quantum phase-slip junctions." IEEE Transactions on Applied Superconductivity 31.5 (2021): 1-8.

[3] Cheng, Ran, Uday S. Goteti, and Michael C. Hamilton. "Spiking neuron circuits using superconducting quantum phase-slip junctions." Journal of Applied Physics 124.15 (2018): 152126.

[4] Hamilton, M. C., Cheng, R., Goteti, U. S., Walker, H., Krause, K. M., & Oeding, L. (2021). Towards Learning in Neuromorphic Circuits Based on Quantum Phase Slip Junctions. *Frontiers in neuroscience*, 1470.

[5] Monroe, D. (2014). Neuromorphic computing gets ready for the (really) big time. *Commun.* ACM 57, 13–15

[6] Mooij, J. and Harmans, C. (2005). Phase-slip flux qubits. *New Journal of Physics* 7, 21

### **Authors Biography**

Harrison Walker is an Auburn graduate with a degree in Materials Engineering. He has utilized the multidisciplinary nature of materials science to research within the College of Electrical and Computer Engineering, fabricating

nanowires to aid in the realization of superconducting neuromorphic hardware. He plans to continue his education by pursuing a PhD at Vanderbilt University in interdisciplinary materials science.

Dr. Michael C. Hamilton received the B.S.E.E. degree from Auburn University in 2000, and the M.S.E.E. and Ph.D. degrees in electrical engineering from The University of Michigan, in 2003 and 2005, respectively.

From 2006 to 2010, he was a member of Technical Staff at MIT-Lincoln Laboratory. In 2010 he joined the Electrical and Computer Engineering Department at Auburn University, where he is now a James B. Davis Professor. In addition to his research group (Auburn Nanosystems Group) at Auburn University, he is the Director of the Alabama Micro/Nano Science and Technology Center (AMNSTC). In 2022, he joined the Google Quantum AI team as a Visiting Faculty Researcher. research interests include His superconducting electronics technologies, microwave superconductivity and packaging/integration technologies for extreme environments (including cryogenic and quantum systems). He has served as the Auburn University IEEE Student Chapter Faculty Advisor, is Chair of MTT-7 Technical Committee on Superconductivity Microwave and Ouantum Technologies, and is an IEEE JMW Topic Editor in the MTT-7 area.